今回はちょっと毛色の違う、最近気になっている事を書いてみようと思う。

各マザーボードベンダーから次期「IvyBridge」アーキテクチャ対応のIntel 7シリーズチップセットを搭載した製品が次々とリリースされるようになった。

一方で、新しいモノ好きでベンチマークの大好きな方々にとって、現行のSandy Bridge-E/4チャンネルメモリアクセス対応のIntel Corei7/3000番シリーズのCPUは価格は別として使ってみたい一品(逸品?)であろう。

特に気になるマザーボードはAsusから発売されているメモリスロットが8本搭載されているP9X79というモデルだ。(このモデルだけではなく、他メーカーにも同様のモデルはある)

CPUソケットを挟んで完全左右対称に4本づつスロット(ソケット)が並んでいる。そしてASUS側では最大64GBのメモリ搭載が可能と保証している。

ここで問題になるのがDDR3/DIMMモジュールの取り付けパターンであり、メモリモジュールの「ランク」という規格である。

ところで、DIMMの「ランク」とは何なのだろうか・・

あまり「これだ」という解りやすいサイトが見当たらないので、あくまで個人的な解釈で解りやすく説明してみたいと思う。

(解り難くても突っ込みは入れないでくだされ~)![]()

まず、「ランク」の事を一般的に理解しやすい「片面/両面実装モジュール」と言う事と同義の様に表現する方がいるが、それはある意味間違いだと思うし、「ランク」を「バンク」と考える事もバンクはDRAMチップ内のセル構成グループの単位で使われたりする為、多少誤解を与える表現だろう。

DIMM(Dual Inline Memory Module)は基本的に64bitのバス幅を持ち、CPUのIMC(メモリコントローラー)やチップセットのMCHに組み込まれたメモリコントローラーはメモリモジュールと直接64bit単位でデータの受け渡しを行う。(アンバッファの場合)

1枚のDIMMの表面(表裏関係無く)には、その64bitの単位を構成するSDRAM(同期型DRAMチップ)の集まり(グループ)が有り、グループが1つ組み込まれたものをシングルランク(1R)モジュールと言い、64bitのグループが2つ組み込まれたものをデュアルランク(2R)モジュールと言う。(チャンネルでは無いので誤解しないように。)

その他にも4つのグループが組み込まれたクアッドランク(4R)モジュールという規格がDDR2 DIMMにはあるが、サーバー用途のECCモジュールに限られる。DDR3規格では現在のところ未定義のようだ。

そして、このグループ(Rank)のチップ構成を決めるのが、各DRAMチップの密度(容量)と各チップから出ている信号線の本数(チップのデータ幅)の相関関係になる。

現在のメインストリームでは、DRAMチップの密度は1Gb(ギガビット)または、2Gbの物が殆どで、バイト換算では各128MB(メガバイト)または256MBの容量のDRAMチップがモジュール上に実装されている。

240PinDIMMの場合、規格上は8Gb(1GB)チップまで開発される予定であり、現在4Gb(512MB)チップは8GBモジュールとして、すでに販売されている。

各DRAMチップからはDDR3の規格上、現時点では8本(x8)又は16本(x16)の信号線が出る事になっていて、各信号線は1bitのデータ幅出力で1チップで合計8bit又は16bitのデータ幅を持つDRAMがある。(DDR2の規格ではDRAMの容量によりx4のチップがある)

以上の事からDDR3アンバッファードDIMM(いわゆる一般のメモリモジュール)で8bitシグナルラインDRAMが使われているDIMMは、64bit÷8bit= 8個のDRAMチップでシングルランク(1R)のグループが形成されている訳だ。

皆さんも手持ちで使っていないDDR3メモリモジュールがあれば見て欲しい。

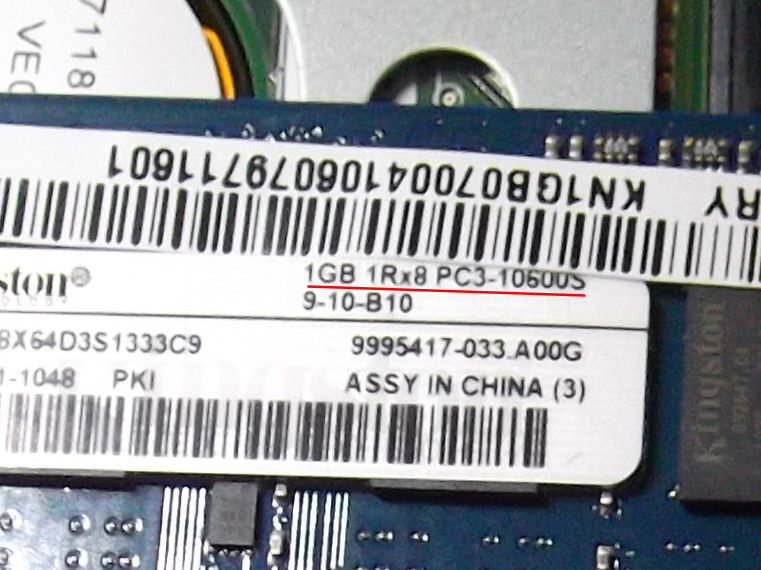

ラベルのモジュール規格の部分に「1Rx8」とか「2Rx8」という表記がされている物があると思う。

1Rx8モジュールの場合、「これはデータ幅8bit(8本の信号線を持った)のDRAMチップを使って1R(ランク/64bit)を形成しているモジュールです」という事になる。

現在のチップ密度とデータ幅から考えると1Rや2Rは「片面/両面」の表記や、「1バンク/2バンク」表記と完全に違っているとは言えない所があるが、正確な表現ではないという事を今後の為に理解しておいた方が良いのではないだろうか・・。

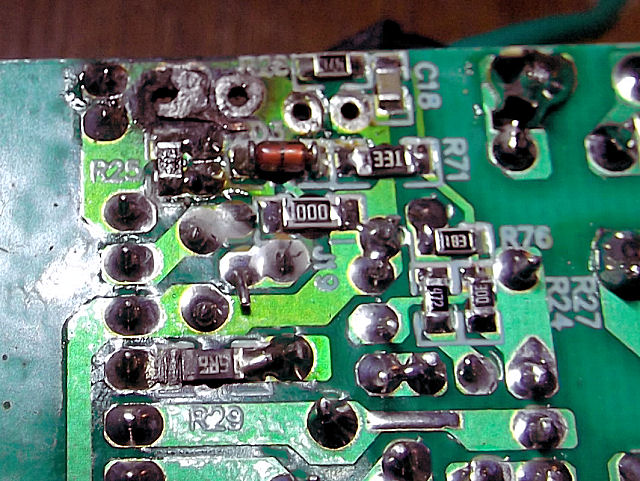

この事がいわゆる「メモリの相性問題」だと勘違いしているユーザーがネットの掲示板を見ていても、とても多い様な気がする。![]()

長くなってしまったので、続きは次回に・・・![]()